存内计算是一类新兴的计算架构。该架构可在存储器阵列内完成逻辑运算,避免存储器和处理器之间频繁的数据搬移操作,从而提升算力,降低功耗。存内计算可分为模拟模式和数字模式。模拟模式可快速实现乘加运算,但计算精度受限,计算和存储的稳定性也较差。数字模式可以保证计算精度,但用于实现复杂逻辑功能时所需的面积较大,性能不佳。崔小乐教授课题组针对数字模式的SRAM存内计算架构开展了系列研究工作。

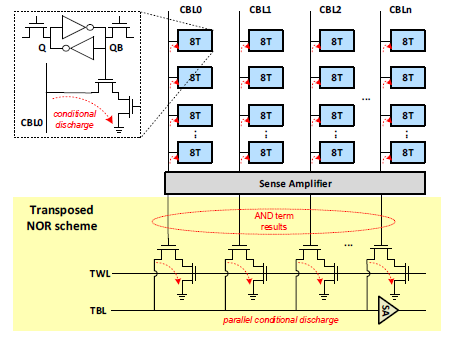

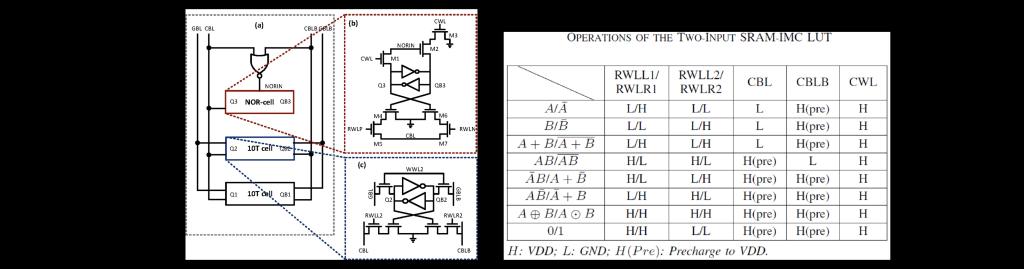

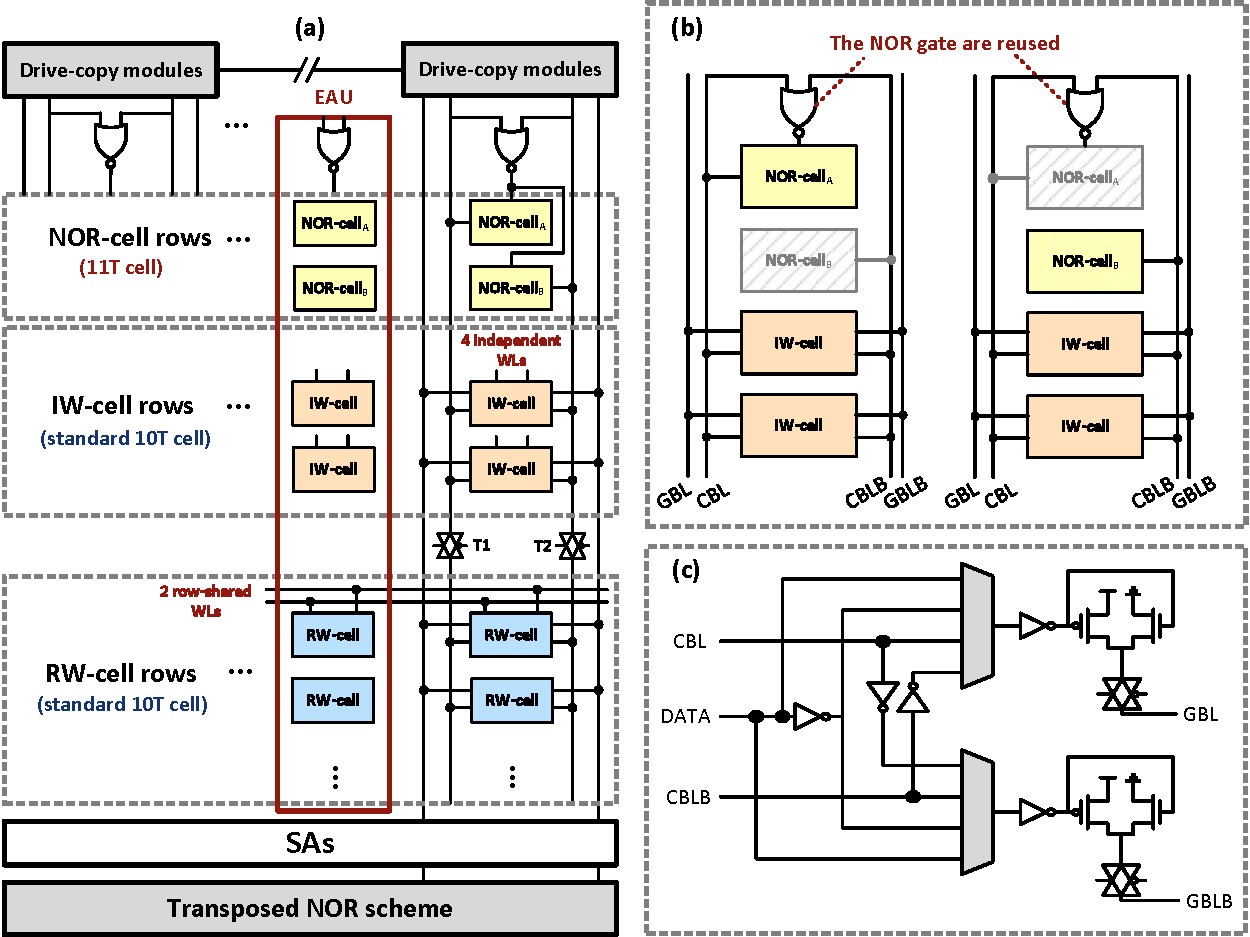

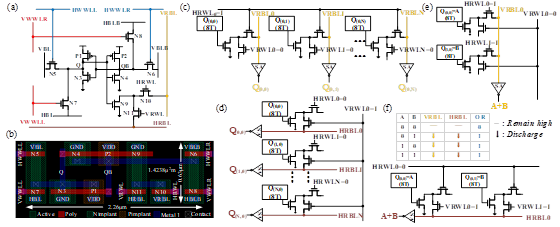

首先,该课题组发现基于SOP(积之和)逻辑形式的SRAM存内计算方案(如图1所示)与基于NOR-NOR(或非-或非)等逻辑形式的计算方案相比具有更好的性能,但面积消耗较多。针对该问题,他们设计了一种基于SRAM的查找表(LUT)电路(如图2所示),用于灵活地在SRAM阵列中实现各种逻辑运算。进而,设计了一种单元异构的SRAM存内计算阵列(如图3所示)。

图1 基于SOP(积之和)逻辑形式的SRAM 存内计算方案

图2 二输入SRAM LUT电路及其支持的逻辑操作

(a)总体结构 (b)NOR单元 (c)10T单元

图3 SRAM存内计算阵列 (a)总体架构 (b)LUT模块 (c)驱动和拷贝模块

针对此存内计算阵列,该课题组提出了将任意逻辑功能映射至该阵列中的方法,并提出了逻辑合并和基于最大图匹配的空间合并等综合技巧,用以降低面积消耗。LGsynth’91,IWLS’93和EPFL等基准电路集合上的综合结果表明,这种在SRAM存内计算阵列上的基于SOP的逻辑综合方法具有高性能、低面积开销的效果。 综合算法的代码已经在IEEE Code Ocean和GitHub平台开源,可供公开下载使用。代码链接为https://codeocean.com/capsule/2304073/tree/v1。

基于这一研究成果的论文《An area-efficient in-memory implementation method of arbitrary Boolean function based on SRAM array》已经于2023年12月在IEEE Transactions on Computers 期刊发表,并被该刊选为本期的Featured Article。博士生张孙睿为论文第一作者。

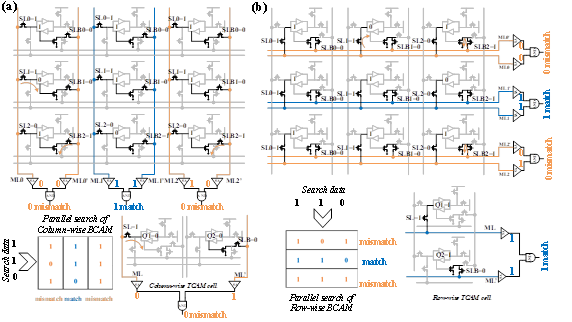

内容寻址存储器(Content-Addressable Memory: CAM)可以将输入数据与存储在阵列内的数据进行比较,并返回匹配数据的地址信息。目前多功能的存内计算SRAM/CAM方案中,CAM的搜索操作都基于阵列的位线BL完成,按列对数据进行搜索匹配。这要求数据被存储在阵列的一列中,与按行进行数据存储的SRAM模式不兼容。

该课题组提出了一种新型的11T SRAM单元(如图4所示)。基于该单元构成的SRAM阵列可工作于四种工作模式,分别为普通读写的SRAM模式、存内逻辑运算的LOGIC模式、BCAM模式和TCAM模式,并且每种工作模式都支持行向和列向的操作(如图5所示)。使用该单元构成阵列,数据可以按行或者按列写进阵列中,行向的SRAM模式与行向的CAM模式兼容,列向的SRAM模式与列向的CAM模式兼容,解决了目前多功能存内计算SRAM/CAM方案中不同工作模式的兼容性问题。此外,该SRAM阵列有利于快速实现矩阵的转置运算。使用者仅需按照一个方向写入数据,按照另一个方向读出数据,即可完成矩阵的转置,从而使原本大运算量的矩阵转置的计算速度大幅提高。

图4. 提出的11T SRAM单元 (a) 原理图 (b) 单元版图 (c) 行向读操作 (d) 列向读操作 (e) 列向逻辑运算操作 (f) 行向逻辑运算操作。

图5. 提出的11T SRAM单元的CAM工作模式 (a) 并行列向BCAM搜索与列向TCAM单元 (b)并行行向搜索与行向TCAM单元。

基于这一研究的论文《An 11T SRAM Cell for the Dual-Direction In-Array Logic/CAM Operations》已被IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II-EXPRESS BRIEFS期刊接收,博士生魏枫为论文第一作者。

这些工作得到了广东省重点领域研发计划项目(2019B010155002)、深圳市学科布局项目(JCYJ20220818100814033)和深圳市孔雀团队项目(KQTD 20200820113105004)等项目的资助,在此表示感谢。

论文列表如下:

[1] S. Zhang, X. Cui, F. Wei and X. Cui, "An Area-Efficient In-Memory Implementation Method of Arbitrary Boolean Function Based on SRAM Array," in IEEE Transactions on Computers, vol. 72, no. 12, pp. 3416-3430, Dec. 2023, doi: 10.1109/TC.2023.3301156.

[2] F. Wei, X. Cui, S. Zhang and X. Zhang, " An 11T SRAM Cell for the Dual-Direction In-Array Logic/CAM Operations," in IEEE Transactions on Circuits and Systems II: Express Briefs , doi: 10.1109/TCSII.2023.3337119.

OA系统

OA系统

公司邮箱

公司邮箱

教务管理

教务管理

资源下载

资源下载

English

English

发布时间:2023-11-30

发布时间:2023-11-30 浏览次数:

浏览次数: