近日,我学院焦海龙课题组(www.PKU-VLSI.com)在集成电路领域顶级期刊IEEE Journal of Solid-State Circuits(JSSC)上发表了题为“An Ultra-Low-Voltage Bit-Interleaved Synthesizable 13T SRAM Circuit”的研究论文(DOI: 10.1109/JSSC.2022.3166944)。该研究摆脱传统存储器中模拟电路带来的局限性,通过设计纯数字存储器电路,并提出与之对应的数字电路设计流程,首次用半定制芯片设计流程实现具有比特交织功能的低功耗静态随机存储器(SRAM)芯片。

随着移动设备、可穿戴设备的日益普及,电子产品的续航能力逐渐成为衡量产品性能的重要指标,电路芯片中低功耗设计问题因此成为国际关注热点。而随着近年来SRAM存储器在芯片功耗占比上的日益提高,低功耗存储器设计成为亟待解决的问题。一方面,传统的存储器因为模拟信号的存在,既影响了功能的稳定性,也限制了芯片通过降低电压的方式实现低功耗的可能性,同时也是造成芯片设计周期长的一个重要原因。另一方面,SRAM存储器中比特交织的结构是保证存储器数据稳定的重要一环,其能通过和芯片上内存维护模块的配合,达到保护芯片数据免受环境噪声影响的目的,保证电子设备的正常功能。

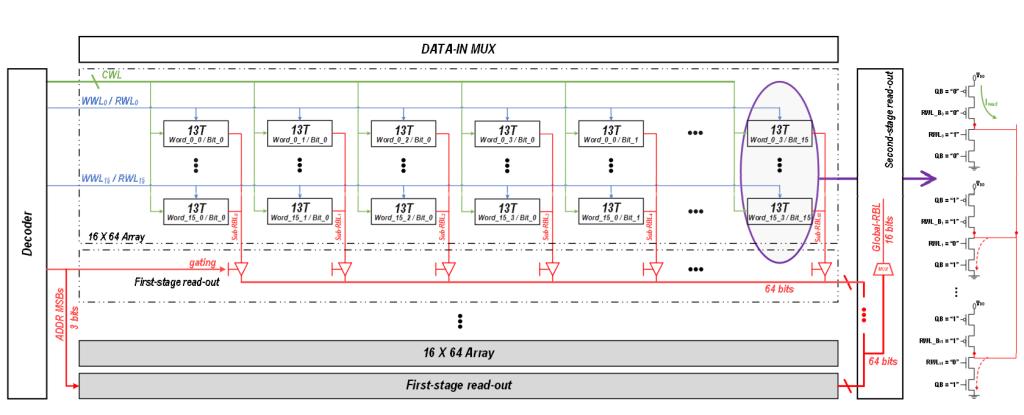

图1 SRAM存储器电路架构图

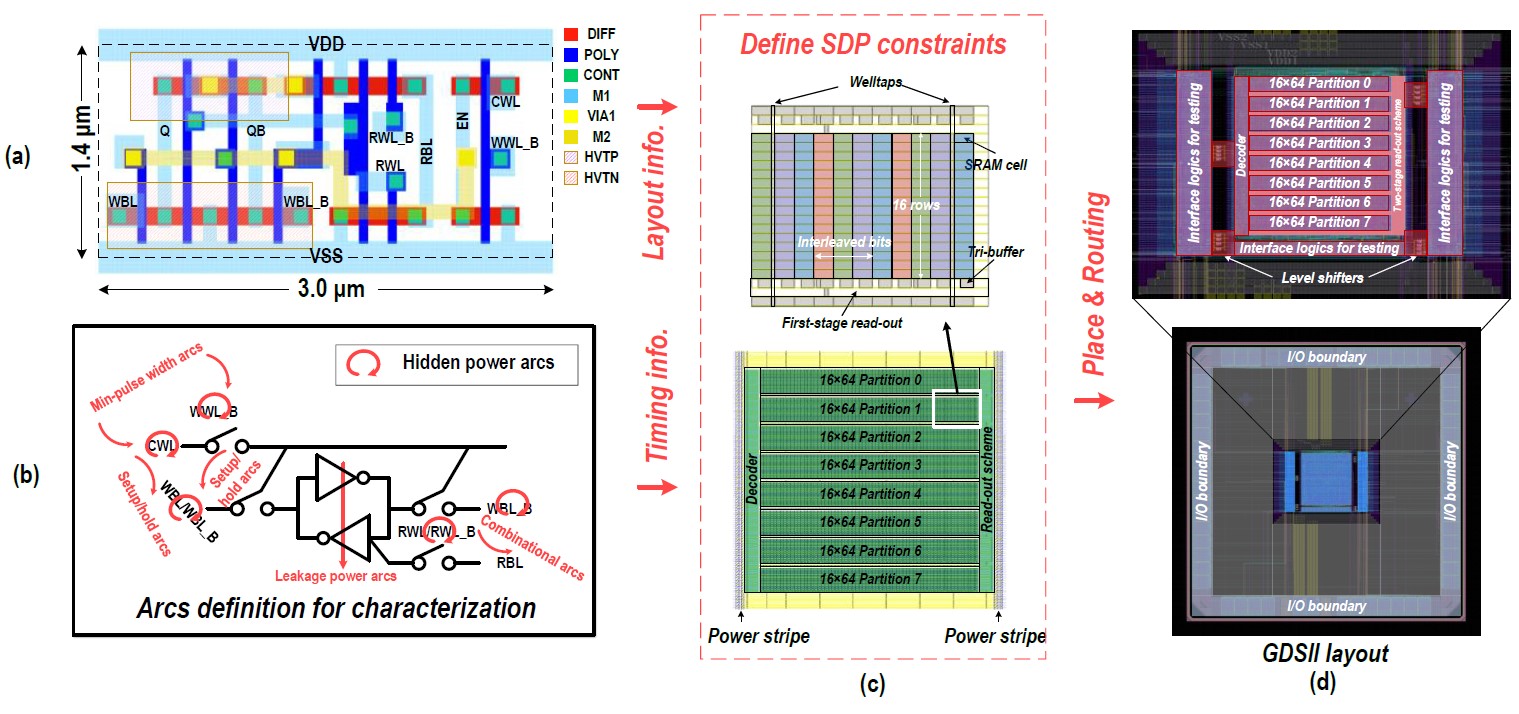

图2 支持比特交织功能的SRAM存储器半定制设计流程

该研究首先提出并实现一种支持比特交织功能的低电压低功耗SRAM存储结构,并且改善了存储电路的结构,优化了芯片的静态功耗和动态功耗。在电路设计中,该研究抛弃了传统存储器中的模拟模块,采用纯数字电路的形式简化了存储器的内部操作,在超低电压下依旧可以保持正常工作,这些都有助于延长芯片整体的续航能力。另外,该研究还提出了与之对应的半定制设计流程。相较于传统的全定制设计流程,该流程在保证比特交织功能的同时,使得存储器的迭代设计周期大大缩短,同时也在存储器设计中引入了更多的设计灵活性,为存内计算AI芯片的设计创造了新的可能性。

JSSC是集成电路领域的顶级学术期刊,也是国际电气电子工程师协会(IEEE)收录最具原创性学术论文的第一旗舰期刊,投稿论文的创新设计必须经过严格的流片验证,大陆地区在JSSC的发文数量常年处于年均个位数的水平。该工作由我学院师生独立完成,焦海龙副教授为论文通讯作者,助理研究员孙家聪为论文第一作者,硕士生李耕和郭浩也对该工作有重要贡献。以上研究工作得到了国家自然科学基金项目和深圳市科技创新委员会的项目支持。

论文链接:https://ieeexplore.ieee.org/document/9764820

(供稿:焦海龙副教授课题组)

OA系统

OA系统

公司邮箱

公司邮箱

教务管理

教务管理

资源下载

资源下载

English

English

发布时间:2022-05-08

发布时间:2022-05-08 浏览次数:

浏览次数: